JEDEC如期的在7月发布了最新版本的LPDDR6(LOW POWER DOUBLE DATA RATE 6)。这也是为了满足包括移动设备和人工智能在内的各种用途的存储器速度和效率而诞生的。

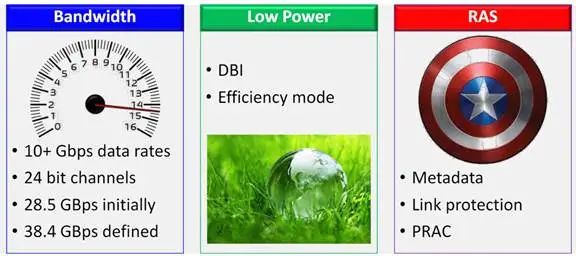

大家都知道,JEDEC各类总线的发展都是在信号速率和功耗上努力,LPDDR6也不例外。LPDDR6这一次升级的重点主要包括了增加带宽、降低功耗和RAS(Reliability, Availability and Serviceability)。随着人工智能和高性能能计算的需求增加,带宽的增加是势在必行的,速率暂时支持12.8Gbps,但是未来会达到14.4Gbps;功耗的降低也是必然趋势,LPDDR6比LPDDR5的功耗降低了。

为了支持 AI 应用和其他高性能工作负载,LPDDR6 采用双子通道架构,可实现灵活的操作,同时保持 32 Bytes小访问单元。

LPDDR6 的主要特性主要有:

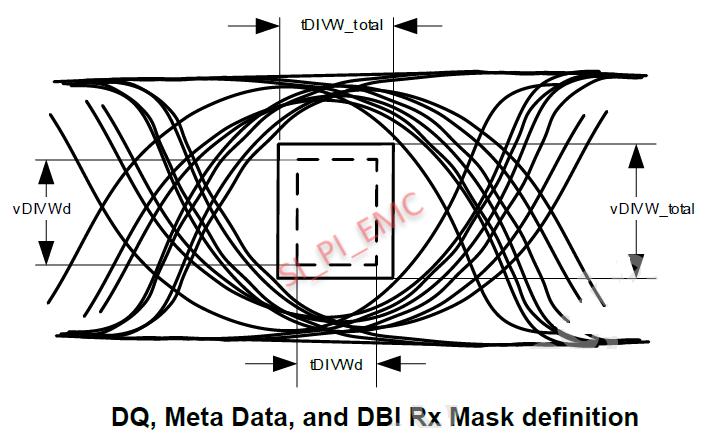

如下所示为DQ/MD/DBI RX的眼图模板定义:

为了满足日益增长的能效需求,在电源方面,LPDDR6 采用比 LPDDR5 更低电压、低功耗的 VDD2 电源供电,并强制使用两个 VDD2 电源。其他节能特性包括:

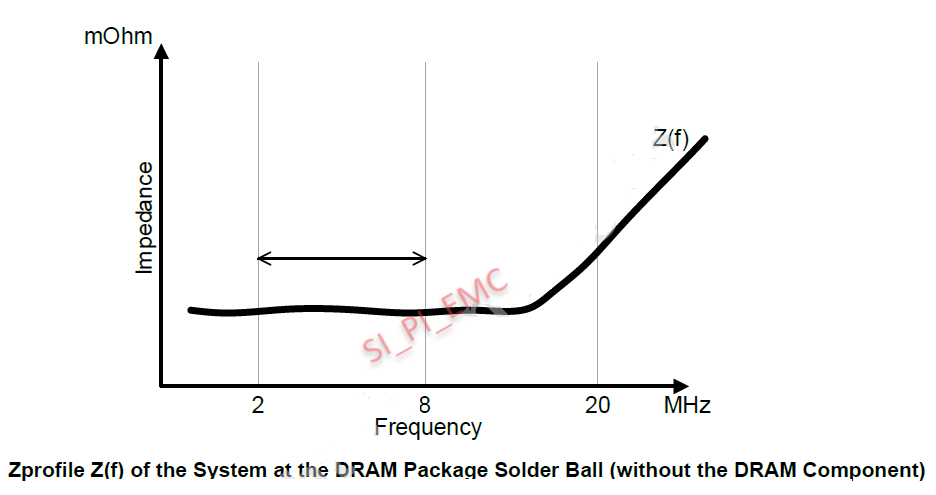

其实,从LPDDR5开始,JEDEC规范对电源完整性就做了比较详细的规定,如下所示为DRAM处的目标阻抗曲线,这对于系统设计工程师/电源完整性工程师而言就有明确的参考规范了。

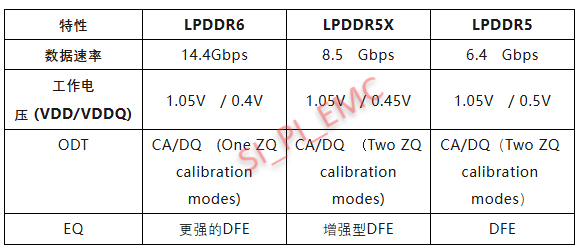

LPDDR6更新的内容非常多,对于硬件工程师和SI/PI工程师来讲,一般比较关注硬件电路的设计和电气参数的变化。我们简单对LPDDR6和LPDDR5/5X做一个对比:

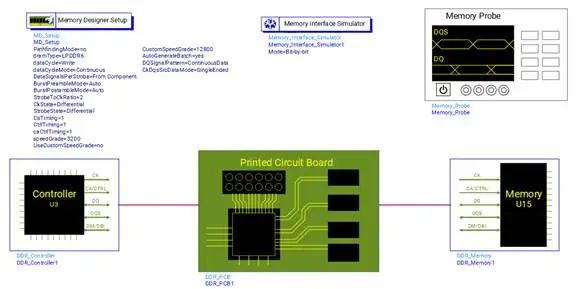

从更新的内容上来看,不管是SI还是PI,其设计难度会更大,毕竟速率越来越高,VDDQ的电压也越来越低。对于仿真来讲的话,由于LPDDR6采用了DFE,所以在高速信号仿真时,需要采用IBIS-AMI模型,仿真方式也没有太多的差异;对于电源完整性的仿真来讲,就没有什么特别的了,做芯片的负责好芯片端,做系统的负责好PCB端即可。在最新版本的ADS中已经支持LPDDR6的信号完整性和电源完整性仿真。